Difference between revisions of "EP2C5T144C8"

From Geeetech Wiki

(→I/O Configuration) |

(→Download Mode) |

||

| Line 15: | Line 15: | ||

== Download Mode == | == Download Mode == | ||

| − | + | '''AS Mode''' | |

| + | <br> | ||

== Resources == | == Resources == | ||

Revision as of 05:58, 9 April 2014

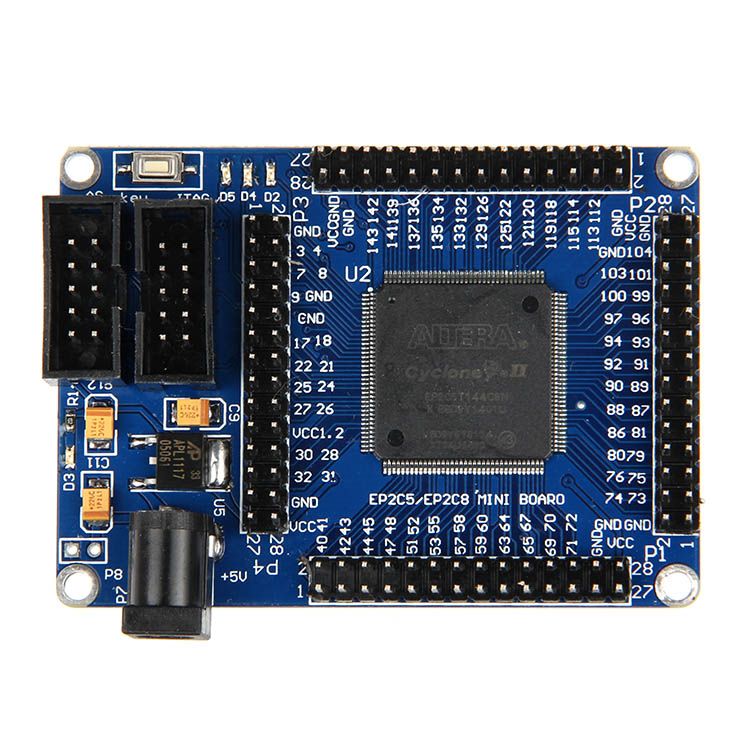

Introduction

The board adopts CycloneIIEP2C5T144 chip of ALERA company as the core,users can easily use the FPGA chip embedded in actual system.The board can complete simple logic control,data acquisition,signal processing,math,etc.The board also support the NiosII embedded development.All the I/O port and the chip clock pin through the row needles to elicit,these interfaces can be extended any memory and peripherals.

I/O Configuration

1、50MHz crystals;

2、LED D2 - Pin3;

3、LED D4 - Pin7;

4、LED D5 - Pin9;

5、Key - Pin144;

Download Mode

AS Mode